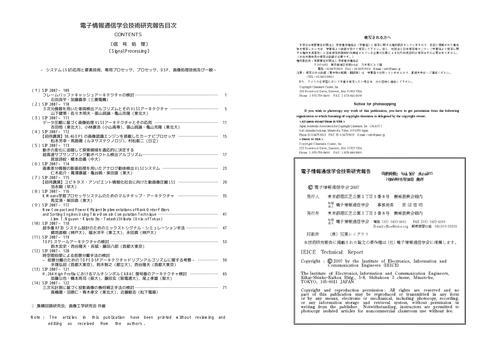

Print edition: ISSN 0913-5685 Online edition: ISSN 2432-6380

[TOP] | [2006] | [2007] | [2008] | [2009] | [2010] | [2011] | [2012] | [Japanese] / [English]

SIP2007-109

A Study of Frame Buffer Cache Architecture

Ryohei Ishida, Yoshiyuki Kato (Mitsubishi Electric Corp.)

pp. 1 - 4

SIP2007-110

Vehicle Detection Algorithm Using Three-Dimensional Information and Its VLSI Architecture

Kensaku Yamashita, Akio Sasaki, Masanori Hariyama, Michitaka Kameyama (Tohoku Univ.)

pp. 5 - 9

SIP2007-111

VLSI Architecture Based on Data Compression and Its Application

Hisashi Yoshida (Tohoku Univ.), Yasuhiro Kobayashi (Oyama National College of Technology), Masanori Hariyama, Michitaka Kameyama (Tohoku Univ.)

pp. 11 - 14

SIP2007-112

[Invited Talk]

-

-, Toru Baji (Renesas), - (Hitachi)

p. 15

SIP2007-113

Super High Speed, Sub-sampling Motion Estimation Algorithm Employing Adaptively Assigned Search Window Sizes

Shimon Isaka, Tadayoshi Enomoto (Chuo Univ.)

pp. 17 - 22

SIP2007-114

An Analog Moving-Object-Localization VLSI System Employing OR-Amplification of Pixel Activities

Yusuke Niki, Yasuo Manzawa, Satoshi Kametani, Tadashi Shibata (Univ. of Tokyo)

pp. 23 - 28

SIP2007-115

[Invited Talk]

-

Takeshi Ikenaga (Waseda Univ.)

pp. 29 - 34

SIP2007-116

A Multiple-Chip Architecture For K-means Learning Processor Systems

Yitao Ma, Tadashi Shibata (Tokyo Univ.)

pp. 35 - 40

SIP2007-117

New Compact and Power-Efficient Implementations of Rank-Order-Filters and Sorting Engines Using Time-Domain Technique

Liem T. Nguyen, Kiyoto Ito, Tadashi Shibata (Univ. of Tokyo)

pp. 41 - 46

SIP2007-118

Mixed-Signal Simulation Methodology for a Highly Collision-Resistive RFID System

Naoki Gochi (Kobe Univ.), Yohei Fukumizu (Tokyo Tech.), Makoto Nagata (Kobe Univ.)

pp. 47 - 51

SIP2007-119

Study on a TOPS scale DSP

Hiroshi Suzuki, Takao Nishitani, Wu Bin, Hachiro Fujita (TMU)

pp. 53 - 58

SIP2007-120

Foreground Segmentation Using Spatio-Temporal Processing

-- A Study on TOPS DSP Architecture Driven Algorithm for Foreground Segmentation --

Hiroaki Tezuka, Tomoyuki Suzuki, Takao Nishitani (Tokyo Metropolitan Univ.)

pp. 59 - 64

SIP2007-121

VLSI Architecture of Multi-Symbol CABAC Decoder for H.264/AVC High Profile

Kimiya Kato, Ryoji Hashimoto (Osaka Univ.), Gen Fujita (Osaka Electro-Comm. Univ.), Takao Onoye (Osaka Univ.)

pp. 65 - 70

SIP2007-122

A Study on Geometric Correction for Projected Images Based on 3D Measurement

Toru Takahashi, Norihito Numa, Takafumi Aoki (Tohoku Univ.), Satoshi Kondo (Matsushita Electric Industrial Co., Ltd.)

pp. 71 - 76

Note: Each article is a technical report without peer review, and its polished version will be published elsewhere.