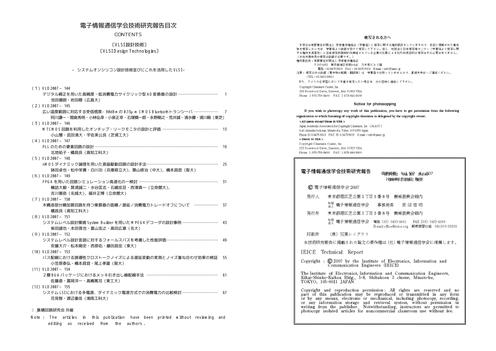

Print edition: ISSN 0913-5685 Online edition: ISSN 2432-6380

[TOP] | [2006] | [2007] | [2008] | [2009] | [2010] | [2011] | [2012] | [Japanese] / [English]

VLD2007-144

A Design of High Accuracy and Low Power Cyclic ADC using Digital Calibration

Tetsuro Ikeda, Atsushi Iwata (Hiroshima Univ.)

pp. 1 - 6

VLD2007-145

A-90dBm Sensitivity 0.13μm CMOS Bluetooth Transceiver Operating in Wide Temperature Range

Kenichi Agawa, Hideaki Majima, Hiroyuki Kobayashi, Masayuki Koizumi, Shinichiro Ishizuka, Takeshi Nagano, Makoto Arai, Yutaka Shimizu, Go Urakawa (Toshiba)

pp. 7 - 12

VLD2007-146

Design and Analysis of on-chip leakage monitor using MTCMOS

Satoshi Koyama, Seidai Takeda, Kimiyoshi Usami (S.I.T.)

pp. 13 - 18

VLD2007-147

Design and Evaluation of the component circuits for the PLL

Yuko Kitaji, Masayoshi Tachibana (Kochi Univ. of Tech.)

pp. 19 - 24

VLD2007-148

Implementation of LCD Driver by nMOS Dynamic Logic

Takuya Hachida, Hideki Matsunaka, Isao Shirakawa (Hyogo Pref. Univ.), Shuji Tsukiyama (Chuo Univ.), Masanori Hashimoto (Osaka Univ.)

pp. 25 - 30

VLD2007-149

A Study for Implementation of High Speed Circuit Simulator by using FPGA

Taiki Hashizume, Seiji Minoura, Tadashi Mizutani, Hironobu Ishijima, Shinichi Nishizawa (Ritsumeikan Univ.), Masaya Yoshikawa (Meijo Univ.), Masahiro Fukui (Ritsumeikan Univ.)

pp. 31 - 36

VLD2007-150

Area/Delay/Power Consumption Tradeoff for Multiplier with Tree-structured Partial-product Adders

Masayoshi Tachibana (kochi University of Technology)

pp. 37 - 42

VLD2007-151

A Case Study on MPEG4 Decoder Design with SystemBuilder

Seiya Shibata, Shinya Honda, Hiroyuki Tomiyama, Hiroaki Takada (Nagoya Univ.)

pp. 43 - 48

VLD2007-152

Performance Estimation considering False-paths for System-level Design

Daisuke Ando, Takeshi Matsumoto, Tasuku Nishihara, Masahiro Fujita (Univ. of Tokyo)

pp. 49 - 54

VLD2007-153

Superposition Effect Validation of Inductive Coupling Noise Based on Measurement of Interconnect Delay Variation

Yasuhiro Ogasahara, Masanori Hashimoto, Takao Onoye (Osaka Univ.)

pp. 55 - 60

VLD2007-154

Global Routing Method of Plating Lead for 2-Layer BGA Packages

Naoki Sato, Yoichi Tomioka, Atsushi Takahashi (Tokyo Tech)

pp. 61 - 66

VLD2007-155

Comparison of Power consumption between dynamic voltage scheme and multi-supply voltage scheme for system LSI

Satoshi Hanami, Shigeyoshi Watanabe (Shonan Inst. of Tech.)

pp. 67 - 72

Note: Each article is a technical report without peer review, and its polished version will be published elsewhere.