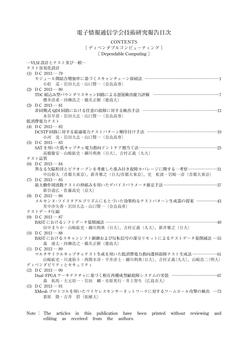

Print edition: ISSN 0913-5685 Online edition: ISSN 2432-6380

[TOP] | [2010] | [2011] | [2012] | [2013] | [2014] | [2015] | [2016] | [Japanese] / [English]

DC2013-79

Module Coupling Overhead Aware Scan Chain Construction

Meguru Komatsu, Hiroshi Iwata, Ken'ichi Yamaguchi (NNCT)

pp. 1 - 5

DC2013-80

On Feasibility of Delay Detection by Time-to-Digital Converter Embedded in Boundary-Scan

Hiroki Sakurai, Hiroyuki Yotsuyanagi, Masaki Hashizume (Univ. of Tokushima)

pp. 7 - 12

DC2013-81

A DFT Method to Achieve 100% Fault Coverage for QDI Asynchronous Circuit

Sanae Mizutani, Hiroshi Iwata, Ken'ichi Yamaguchi (NNCT)

pp. 13 - 18

DC2013-82

Suitable Power-Aware Test Pattern Ordering for Deterministic Circular Self Test Path

Ryo Ogawa, Hiroshi Iwata, Ken'ichi Yamaguchi (NNCT)

pp. 19 - 24

DC2013-83

A Low Power Dissipation Oriented Don't Care Filling Method Using SAT

Yoshiyasu Takahashi, Hiroshi Yamazaki, Toshinori Hosokawa (Nihon Univ.), Masayoshi Yoshimura (Kyushu Univ)

pp. 25 - 30

DC2013-84

Note on Weighted Fault Coverage Considering Multiple Defect Sizes and Via Open

Yuta Nakayama (Tokyo Metro. Univ.), Masayuki Arai (Nihon Univ.), Hongbo Shi, Kazuhiko Iwasaki (Tokyo Metro. Univ.)

pp. 31 - 36

DC2013-85

Device-parameter Estimation Using Framework of Fmax Testing

Michihiro Shintani, Takashi Sato (Kyoto Univ.)

pp. 37 - 42

DC2013-86

An Efficient Test Pattern Generator based on Mersenne Twister algorithm

Sayaka Satonaka, Hiroshi Iwata, Ken'ichi Yamaguchi (NNCT)

pp. 43 - 48

DC2013-87

A reduction method of shift data volume on BAST

Marika Tanaka, Hiroshi Yamazaki, Toshinori Hosokawa (Nihon Univ), Masayoshi Yoshimura (Kyushu Univ), Masayuki Arai (Nihon Univ)

pp. 49 - 54

DC2013-88

Test Data Reduction Method for BIST-Aided Scan Test by Controlling Scan Shift and Partial Reset of Inverter Code

Ryota Mori, Hiroyuki Yotsuyanagi, Masaki Hashizume (Univ. of Tokushima)

pp. 55 - 60

DC2013-89

A Low Power Consumption Oriented Test Generation Method for Transition Faults Using Multi Cycle Capture Test Generation

Hiroshi Yamazaki, Yuto Kawatsure, Jun Nishimaki, Atsushi Hirai, Toshinori Hosokawa (Nihon Univ), Masayoshi Yoshimura (Kyushu Univ), Koji Yamazaki (Meiji Univ)

pp. 61 - 66

DC2013-90

An Implementation of Fault Tolerant Systems with Mutual Reconfiguration Based on Dual-FPGA Architecture

Takuma Mori, Shoichi Ohmoto, Tsuyoshi Iwagaki, Hideyuki Ichihara, Tomoo Inoue (Hiroshima City Univ.)

pp. 67 - 72

DC2013-91

Detection of Wormhole Attack in Wireless Sensor Network with XMesh Protocol

Takashi Minohara, Aoi Yoshii (Takushoku Univ.)

pp. 73 - 78

Note: Each article is a technical report without peer review, and its polished version will be published elsewhere.