Print edition: ISSN 0913-5685 Online edition: ISSN 2432-6380

[TOP] | [2015] | [2016] | [2017] | [2018] | [2019] | [2020] | [2021] | [Japanese] / [English]

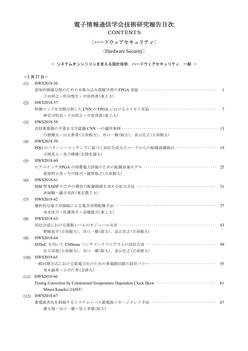

HWS2018-56

FPGA Implementation of Fully Convolutional Network for Semantic Segmentation

Masayuki Shimoda, Youki Sada, Hiroki Nakahara (titech)

pp. 1 - 6

HWS2018-57

Spatial-Separable Convolution: Low memory CNN for FPGA

Akira Jinguji, Masayuki Shimoda, Hiroki Nakahara (titech)

pp. 7 - 12

HWS2018-58

A Case Study on Approximate Multipliers for MNIST CNN

Kenta Shirane, Takahiro Yamamoto (Ritsumeikan Univ.), Ittetsu Taniguchi (Osaka Univ.), Hiroyuki Tomiyama (Ritsumeikan Univ.)

pp. 13 - 18

HWS2018-59

Pattern Matching Based Detection of Wire Congestion from Source Code Description for High Level Synthesis

Masato Tatsuoka, Mineo Kaneko (JAIST)

pp. 19 - 24

HWS2018-60

Wire Load Model for Power Consumption Evaluation of Via-Switch FPGA

Asuka Natsuhara, Takashi Imagawa, Hiroyuki Ochi (Ritsumeikan Univ.)

pp. 25 - 30

HWS2018-61

Routing Algorithm to Achieve Circular Wire for SIM-Type SADP

Shun Akatsuka, Kunihiro Fujiyoshi (TUAT)

pp. 31 - 36

HWS2018-62

Set-Pair Routing Algorithm with Selective Pin-Pair Connections

Kano Akagi, Shimpei Sato, Atsushi Takahashi (Tokyo Tech)

pp. 37 - 42

HWS2018-63

Function-level Module Sharing with High-level Synthesis

Ryohei Nozaki (Ritsumeikan Univ.), Ittetsu Taniguchi (Osaka Univ.), Hiroyuki Tomiyama (Ritsumeikan Univ.)

pp. 43 - 48

HWS2018-64

High-Level Synthesis of the CHStone Benchmark Programs with SDSoC

Takuya Adachi (Ritsumeikan Univ.), Ittetsu Taniguchi (Osaka Univ.), Hiroyuki Tomiyama (Ritsumeikan Univ.)

pp. 49 - 54

HWS2018-65

Design Flow of Circuits with Multiple Supply Voltages for Power Reduction in General-Synchronous Framework

Masataka Aoki, Yukihide Kohira (Univ. of Aizu)

pp. 55 - 60

HWS2018-66

Timing Correction by Constrained Temperature Dependent Clock Skew

Mineo Kaneko (JAIST)

pp. 61 - 66

HWS2018-67

A Battery Degradation aware System Level Battery Management Methodology

Daichi Watari, Ittetsu Taniguchi, Takao Onoye (Osaka Univ.)

pp. 67 - 72

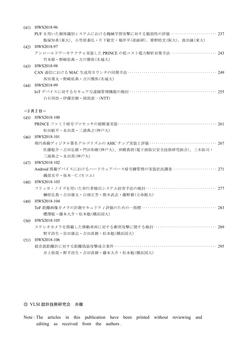

HWS2018-68

Design of an FPGA-based Manycore Architecture with Selective Local/Global Memory

Seiya Shirakuni (Ritsumeikan Univ.), Ittetsu Taniguchi (Osaka Univ.), Hiroyuki Tomiyama (Ritsumeikan Univ.)

pp. 73 - 78

HWS2018-69

Improvement on DMA Transfer Efficiency by Packet Concatenation

Shoko Ohteru, Saki Hatta, Tomoaki Kawamura, Koji Yamazaki, Takahiro Hatano, Akihiko Miyazaki, Koyo Nitta (NTT)

pp. 79 - 84

HWS2018-70

Thermal transient analysis and evaluation of the heat generation and dissipation in three-dimensional stacked LSI

Ryota Horigome, Kimiyoshi Usami (Shibaura Inst. of Tech.)

pp. 85 - 90

HWS2018-71

Evaluation of low power consumption Standard Cell Memory (SCM) using body-bias control in Silicon-on-Thin-BOX MOSFET:SOTB

Ryo Magasaki, Yusuke Yoshida (Shibaura Inst. of Tech.), Hideharu Amano (Keio Univ.), Kimiyoshi Usami (Shibaura Inst. of Tech.)

pp. 91 - 96

HWS2018-72

Single Supply Level Shifter Circuit using body-bias

Yuki Takeyoshi, Kimiyoshi Usame (SIT)

pp. 97 - 102

HWS2018-73

Implementation Technology for the Advanced Wafer Manufacturing Processes on Optical Transmission LSIs

Susumu Hirano, Hideo Yoshida, Kenya Sugihara, Yoshiaki Konishi, Takashi Sugihara, Yoshihiro Ogawa (Mitsubishi Electric)

pp. 103 - 108

HWS2018-74

*

Yuka Aizawa, Masashi Tawada (Waseda Univ.), Yuta Ideguchi, Norifumi Kamiya (NEC), Nozomu Togawa (Waseda Univ.)

pp. 109 - 114

HWS2018-75

High-Speed and Noise-Tolerant High-Radix Tree Domino Adder Targeted to 65 nm FD-SOI Technology

Kazuki Niino, Takashi Imagawa, Hiroyuki Ochi (Ritsumeikan Univ.)

pp. 115 - 120

HWS2018-76

Selection of Gaussian Mixture Reduction Methods Using Machine Learning

Haruki Kazama, Shuji Tsukiyama (Chuo Univ.)

pp. 121 - 126

HWS2018-77

Model Compression for ECG Signals Outlier Detection Hardware trained by Sparse Robust Deep Autoencoder

Naoto Soga, Shimpei Sato, Hiroki Nakahara (Titech)

pp. 127 - 132

HWS2018-78

[Memorial Lecture]

Towards Practical Homomorphic Email Filtering: A Hardware-Accelerated Secure Naive Bayesian Filter

Song Bian, Masayuki Hiromoto, Takashi Sato (Kyoto Univ.)

pp. 133 - 138

HWS2018-79

[Memorial Lecture]

Methods for Reducing Power and Area of BDD-based Optical Logic Circuits

Ryosuke Matsuo, Jun Shiomi, Tohru Ishihara, Hidetoshi Onodera (Kyoto Univ.), Akihiko Shinya, Masaya Notomi (NTT)

pp. 139 - 144

HWS2018-80

A SPICE Model Parameter Extraction Environment Using Automatic Differentiation

Aoi Ueda (NNCT), Michihiro Shintani (NAIST), Hiroshi Iwata, Ken'ichi Yamaguchi (NNCT), Michiko Inoue (NAIST)

pp. 145 - 150

HWS2018-81

An Algorithm to Determine Circuit Model Parameters for Electric Double-Layer Capacitor

Naoki Kosaka, Shuji Tsukiyama (Chuo Univ.), Kenichi Noto, Takuji Okumura (Komatsu Ltd.)

pp. 151 - 156

HWS2018-82

Design of High-Speed Gaussian Sampler Using Micciancio-Walter Algorithm

Keitaro Koga (UTokyo), Hiromitsu Awano (Osaka Univ.), Makoto Ikeda (UTokyo)

pp. 157 - 162

HWS2018-83

Fundamental Study on Individual Identification Method of Electronic Device Using Difference of Radiation Spectrum Caused by Manufacturing/Mounting Variations

Shugo Kaji (NAIST), Masahiro kinugawa (NIT), Daisuke Fujimoto (NAIST), Laurent Sauvage, Jean-Luc Danger (Telecom ParisTech), Yu-ichi Hayashi (NAIST)

pp. 163 - 167

HWS2018-84

Error correction method for PUF utilizing the Pixel Variation in the CMOS Image Sensor

Ryota Ishiki, Masayoshi Shirahata (Ritsumeikan Univ.), Shunsuke Okura (Brillnics), Mitsuru Shiozaki, Takaya Kubota (Ritsumeikan Univ.), Kenichiro Ishikawa, Isao Takayanagi (Brillnics), Takeshi Fujino (Ritsumeikan Univ.)

pp. 169 - 174

HWS2018-85

Synthesis of Full Hardware Implementation of RTOS-Based Systems

Yuuki Oosako, Nagisa Ishiura (Kwansei Gakuin Univ.), Hiroyuki Tomiyama (Ritsumeikan Univ.), Hiroyuki Kanbara (ASTEM)

pp. 175 - 180

HWS2018-86

A Study on Placement Constraints for Asynchronous Circuits with Bundled-data Implementation aimed for FPGAs

Tatsuki Otake, Hiroshi Saito (UoA)

pp. 181 - 186

HWS2018-87

Reinforcing Generation of Instruction Sequences in Random Testing of Android Virtual Machine

Ryotaro Shimizu, Nagisa Ishiura (Kwansei Gakuin Univ.)

pp. 187 - 192

HWS2018-88

Synthesis of Distributed Control Circuits for Dynamic Scheduling across Multiple Dataflow Graphs

Sayuri Ota, Nagisa Ishiura (Kwansei Gakuin Univ.)

pp. 193 - 198

HWS2018-89

On evaluation of an efficient SAT attack algorithm for logic encryption

Yusuke Matsunaga (Kyushu Univ.), Masayoshi Yoshimura (Kyoto Sangyou Univ.)

pp. 199 - 204

HWS2018-90

A Study on Quantized HOG Calculation suitable for Hardware Implementation

Yusuke Sekiguchi, Yoichi Tomioka, Junji Kitamichi (UoA.)

pp. 205 - 210

HWS2018-91

Energy-Efficient, Small-Scale Multicore Processor towards IoT Edge Computing

Sayuri Onagi, Kaoru Saso, Yuko Hara-Azumi (Tokyo Tech.)

pp. 211 - 216

HWS2018-92

Embedded Systems Designs Using Approximate Computing for Data Clustering Acceleartion

Shun Kimijima, Fransiscus Marcel Satria, Yuko Hara-Azumi (Tokyo Tech.)

pp. 217 - 222

HWS2018-93

Integrated Circuit Design and Evaluation of Chip-Package-Board Interactive PUF Based on Wireless Chaos Oscillation

Masanori Takahashi, Makoto Nagata, Noriyuki Miura (Kobe Univ.)

pp. 223 - 224

HWS2018-94

Performance and Security Evaluation of Ring Oscillator PUF Implemented on ASIC

Yusuke Nozaki, Masaya Yoshikawa (Meijo Univ.)

pp. 225 - 230

HWS2018-95

An Attack with Linear Model Against Improved Arbiter PUF

Susumu Matsumi, Yusuke Nozaki, Masaya Yoshikawa (Meijo Univ.)

pp. 231 - 236

HWS2018-96

On Machine Learning Attack Tolerance for PUF-based Device Authentication System

Tomoki Iizuka (UTokyo), Yasuhiro Ogasahara, Toshihiro Katashita, Yohei Hori (AIST), Hiromitsu Awano (Osaka Univ.), Makoto Ikeda (UTokyo)

pp. 237 - 242

HWS2018-97

Low-Cost Power Analysis Countermeasures for Unrolled Architecture Implementation PRINCE

Shu Takemoto, Yusuke Nozaki, Masaya Yoshikawa (Meijo Univ.)

pp. 243 - 248

HWS2018-98

A Counter Synchronization Method for MAC generation in CAN Communication

Kanata Nishida, Yusuke Nozaki, Masaya Yoshikawa (Meijo Univ.)

pp. 249 - 254

HWS2018-99

An Extended of Secure Remote Management Architecture for IoT-device

Masahiro Shiraishi, Hiroki Ito, Keiichi Okabe (NTT)

pp. 255 - 260

HWS2018-100

An ultra-light weight implementation of PRINCE-family cryptographic processor

Kohei Matsuda, Makoto Nagata, Noriyuki Miura (Kobe Univ.)

pp. 261 - 265

HWS2018-101

ASIC Chip Implementation and Evaluation of Elliptic Curve Digital Signature Algorithm

Sosuke Sato, Hiroki Yoshida, Kazuki Monta (Kobe Univ.), Takaaki Okidono (ECSEC), Takuji Miki, Noriyuki Miura, Makoto Nagata (Kobe Univ.)

pp. 267 - 269

HWS2018-102

A Report on Adoption Rates of Android Devices Implemented Hardware-backed Key Management

Kohei Isobe, Takahito Sakamoto (SECOM)

pp. 271 - 276

HWS2018-103

A study of interference method using flicker noise for a pedestrian detection system

Hirotaka Sakakibara, Kota Yoshida, Masayoshi Shirahata, Takeshi Kumaki, Takeshi Fujino (Ritsumeikan Univ)

pp. 277 - 282

HWS2018-104

An Instrumentation Security Metric for ToF Depth-Image Cameras

Satoru Sakurazawa, Daisuke Fujimoto, Tsutomu Matsumoto (YNU)

pp. 283 - 288

HWS2018-105

A Study of Collision Attacks on Moving Vehicle Equipped with Stereo Vision Camera

Hiroki Nohira, Yasushi Iwata, Naoki Yoshida, Tsutomu Matsumoto (YNU)

pp. 289 - 293

HWS2018-106

Conditions for Successful Attacks on Ultrasonic Range Finder to Output Incorrect Values

Yuya Inoue, Hiroki Nohira, Naoki Yoshida, Daisuke Fujimoto, Tsutomu Matumoto (YNU)

pp. 295 - 299

Note: Each article is a technical report without peer review, and its polished version will be published elsewhere.