Print edition: ISSN 0913-5685 Online edition: ISSN 2432-6380

[TOP] | [2016] | [2017] | [2018] | [2019] | [2020] | [2021] | [2022] | [Japanese] / [English]

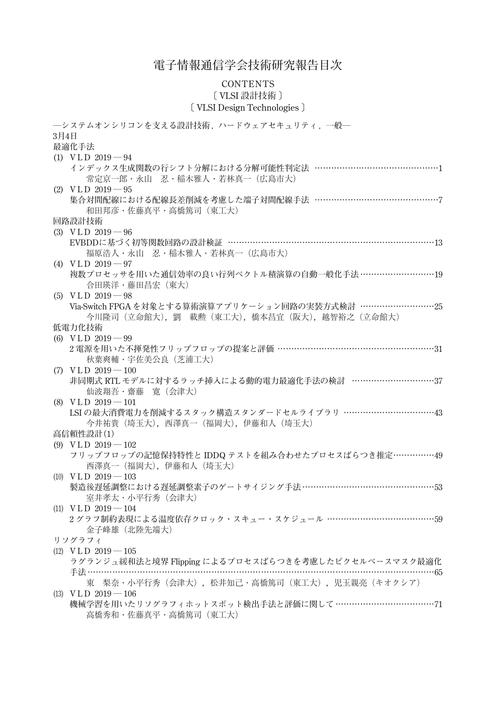

VLD2019-94

インデックス生成関数の行シフト分解における分解可能性判定法

○常定京一郎・永山 忍・稲木雅人・若林真一(広島市大)

pp. 1 - 6

VLD2019-95

集合対間配線における配線長差削減を考慮した端子対間配線手法

○和田邦彦・佐藤真平・高橋篤司(東工大)

pp. 7 - 12

VLD2019-96

EVBDDに基づく初等関数回路の設計検証

○福原浩人・永山 忍・稲木雅人・若林真一(広島市大)

pp. 13 - 18

VLD2019-97

複数プロセッサを用いた通信効率の良い行列ベクトル積演算の自動一般化手法

○合田瑛洋・藤田昌宏(東大)

pp. 19 - 24

VLD2019-98

Via-Switch FPGAを対象とする算術演算アプリケーション回路の実装方式検討

○今川隆司(立命館大)・劉 載勲(東工大)・橋本昌宜(阪大)・越智裕之(立命館大)

pp. 25 - 29

VLD2019-99

2電源を用いた不揮発性フリップフロップの提案と評価

○秋葉爽輔・宇佐美公良(芝浦工大)

pp. 31 - 36

VLD2019-100

非同期式RTLモデルに対するラッチ挿入による動的電力最適化手法の検討

○仙波翔吾・齋藤 寛(会津大)

pp. 37 - 42

VLD2019-101

LSIの最大消費電力を削減するスタック構造スタンダードセルライブラリ

○今井祐貴(埼玉大)・西澤真一(福岡大)・伊藤和人(埼玉大)

pp. 43 - 48

VLD2019-102

フリップフロップの記憶保持特性とIDDQテストを組み合わせたプロセスばらつき推定

○西澤真一(福岡大)・伊藤和人(埼玉大)

pp. 49 - 52

VLD2019-103

製造後遅延調整における遅延調整素子のゲートサイジング手法

○室井孝太・小平行秀(会津大)

pp. 53 - 58

VLD2019-104

2グラフ制約表現による温度依存クロック・スキュー・スケジュール

○金子峰雄(北陸先端大)

pp. 59 - 64

VLD2019-105

ラグランジュ緩和法と境界Flippingによるプロセスばらつきを考慮したピクセルベースマスク最適化手法

○東 梨奈・小平行秀(会津大)・松井知己・高橋篤司(東工大)・児玉親亮(キオクシア)

pp. 65 - 70

VLD2019-106

機械学習を用いたリソグラフィホットスポット検出手法と評価に関して

○高橋秀和・佐藤真平・高橋篤司(東工大)

pp. 71 - 76

VLD2019-107

リソグラフィホットスポット検出用既存訓練データの修正による訓練データの追加生成

○片岡 岳・稲木雅人・永山 忍・若林真一(広島市大)

pp. 77 - 82

VLD2019-108

リソグラフィホットスポット検出のための画像スペクトルに基づく特徴量についての一検討

○稲木雅人・片岡 岳・永山 忍・若林真一(広島市大)

pp. 83 - 88

VLD2019-109

ドローンによる配送計画問題に対するモンテカルロ木探索手法

○岩﨑宏太・高島康裕(北九州市大)

pp. 89 - 94

VLD2019-110

HCP: History-based Congestion Prediction Algorithm for Network-on-Chip

○Zhenyu Hu・Michael Conrad Meyer(Waseda Univ.)・Xin Jiang(NITKIT)・Takahiro Watanabe(Waseda Univ.)

pp. 95 - 100

VLD2019-111

電流兆候解析に基づくDCモーターのオンライン故障検知

○大窄直樹(関西学院大)・神原弘之(京都高度技研)・石浦菜岐佐(関西学院大)

pp. 101 - 106

VLD2019-112

チェックサムとオンラインテストによるメモリスタニューラルネットワークの耐故障設計

○石坂 守・新谷道広・井上美智子(奈良先端大)

pp. 107 - 112

VLD2019-113

遅延故障に起因する回路寿命分布の確率的高速推定手法

○富山葉月・増田 豊・石原 亨(名大)

pp. 113 - 118

VLD2019-114

プログラマブルSoCにおけるErlangからのハードウェア制御

○若林秀和・石浦菜岐佐(関西学院大)

pp. 119 - 124

VLD2019-115

Neural Programmer-Interpreters による実行形式の生成を目指した研究

○津山雅彦・宮本龍介(明大)

pp. 125 - 130

VLD2019-116

システムリソースを有効活用したH/W-S/W協調設計支援手法

○輕部文利・立見駿介・岡田尚也・山本 亮・小川吉大(三菱電機)・ゴールドスミス アブラハム・クリネン リエン(MERL)

pp. 131 - 136

VLD2019-117

[記念講演]Small-Area and Low-Power FPGA-Based Multipliers using Approximate Elementary Modules

○Yi Guo・Heming Sun・Shinji Kimura(Waseda Univ.)

p. 137

VLD2019-118

[記念講演]A Tuning-Free Hardware Reservoir Based on MOSFET Crossbar Array for Practical Echo State Network Implementation

○Yuki Kume・Song Bian・Takashi Sato(Kyoto Univ.)

pp. 139 - 144

VLD2019-119

[記念講演]Workload-aware Data-eviction Self-adjusting System of Multi-SCM Storage to Resolve Trade-off between SCM Data-retention Error and Storage System Performance

○Reika Kinoshita・Chihiro Matsui・Atsuya Suzuki・Shouhei Fukuyama・Ken Takeuchi(Chuo Univ.)

pp. 145 - 150

VLD2019-120

Approximate Floating Point Multiplier based on Shifting Addition Using Carry Signal from Second-Highest-Bit

○Jie Li・Yi Guo・Shinji Kimura(Waseda Univ.)

pp. 151 - 156

VLD2019-121

直近計算結果に基づくApproximate Computingを用いた画像のエッジ検出手法の提案と有効性評価

○尾地 肇・宇佐美公良(芝浦工大)

pp. 157 - 162

VLD2019-122

乱数化関数を用いた乱数生成回路を共有するストカスティック数生成器

○多和田雅師・戸川 望(早大)

pp. 163 - 166

VLD2019-123

イジングマシンを用いたアミューズメントパークの経路最適化手法

○武笠陽介・若泉朋弥・田中 宗・戸川 望(早大)

pp. 167 - 172

VLD2019-124

イジング計算機による3次元直方体パッキング問題の解法

○金丸 翔・寺田晃太朗・川村一志・田中 宗(早大)・富田憲範(富士通研)・戸川 望(早大)

pp. 173 - 178

VLD2019-125

Isolation Forestによる異常検知の効率化に関する検討

○池田 翼・永山 忍・稲木雅人・若林真一(広島市大)

pp. 179 - 184

VLD2019-126

選択的な低処理遅延データ圧縮による高バンド幅相互結合網

○丹羽直也(慶大)・平澤将一・鯉渕道紘(NII)・天野英晴(慶大)

pp. 185 - 190

VLD2019-127

ハードウェアアクセラレータ内蔵仮想化対応トラフィック監視システムの開発

○池田奈美子・右近祐太・大輝晶子・吉田周平・新田高庸(NTT)

pp. 191 - 196

VLD2019-128

順序回路への故障注入に起因した不均一な頻度分布を持つ誤り出力を用いた故障利用解析

○岡本拓実・藤本大介(奈良先端大)・崎山一男・李 陽(電通大)・林 優一(奈良先端大)

pp. 197 - 201

VLD2019-129

無線通信ICに対するサイドチャネル攻撃の基礎検討

○一ノ瀬竜矢・坂本純一・松本 勉(横浜国大)

pp. 203 - 207

VLD2019-130

Fp256楕円曲線暗号の高速化に向けた設計空間探索

○池田健人・池田 誠(東大)

pp. 209 - 214

VLD2019-131

パーシャルMAX-SATを用いた抵抗性オープン故障に対するテスト生成法

○山崎紘史・石山悠太・松田竜馬・細川利典(日大)・吉村正義(京都産大)・新井雅之(日大)・四柳浩之・橋爪正樹(徳島大)

pp. 215 - 220

VLD2019-132

アフィン変換を用いた論理暗号化手法の評価

○松永裕介(九大)

pp. 221 - 225

VLD2019-133

トリガ回路の性質にもとづく特徴量を利用したニューラルネットワークによるハードウェアトロイ識別

○井上智貴・長谷川健人・戸川 望(早大)

pp. 227 - 232

VLD2019-134

ゼロビットスキップ機能付きビットシリアル内積回路を用いた畳み込み演算の高速化に関する一検討

○磯部 宙・富岡洋一(会津大)

pp. 233 - 238

VLD2019-135

制御機器におけるDeep Neural NetworkのFPGA向け回路アーキテクチャの検討

○山本 亮・岩河秀知・小川吉大(三菱電機)

pp. 239 - 244

VLD2019-136

2つのMOSFETリザバー用いたエコーステートネットワークの性能評価

○久米祐貴・辺 松・名倉健太・佐藤高史(京大)

pp. 245 - 250

VLD2019-137

ニューラルネットワークの集積ナノフォトニクス実装に適した回路構造探索

○服部直樹・増田 豊・石原 亨(名大)・塩見 準(京大)・新家昭彦・納富雅也(NTT)

pp. 251 - 256

VLD2019-138

Non-IID PUFのエントロピー低下要因とエントロピー見積もり手法 (1)

○汐﨑 充(立命館大)・堀 洋平(産総研)・大倉俊介・白畑正芳・藤野 毅(立命館大)

pp. 257 - 262

VLD2019-139

Non-IID PUFのエントロピー低下要因とエントロピー見積もり手法 (2)

○汐﨑 充(立命館大)・堀 洋平(産総研)・大倉俊介・白畑正芳・藤野 毅(立命館大)

pp. 263 - 268

VLD2019-140

車線検出機能に対する色調改変攻撃

○宮園史規・吉田直樹・松本 勉(横浜国大)

pp. 269 - 274

VLD2019-141

誘導インパルス型の瞬時自己破壊回路を利用した検知後対処に基づく物理攻撃対策

○多田 捷・松田航平・永田 真(神戸大)・﨑山一男(電通大)・三浦典之(神戸大)

pp. 275 - 277

VLD2019-142

ICチップレベル電源雑音シミュレーションによる暗号モジュールのサイドチャネル漏洩評価

○安田一樹・門田和樹・月岡暉裕・三浦典之・永田 真(神戸大)・カシーク スリニバサン・シャン ワン・ラン リン・イン シュン リー・ノーマン チャン(アンシス)

pp. 279 - 282

VLD2019-143

暗号回路における基板電流検出型レーザー故障注入攻撃対策の軽量設計法

○山下憂記・松田航平・永田 真・三浦典之(神戸大)

pp. 283 - 284

VLD2019-144

完全準同型暗号のハードウェア向けアルゴリズムとアーキテクチャ設計

○杉山昇太郎・池田 誠(東大)

pp. 285 - 290

注: 本技術報告は査読を経ていない技術報告であり,推敲を加えられていずれかの場に発表されることがあります.