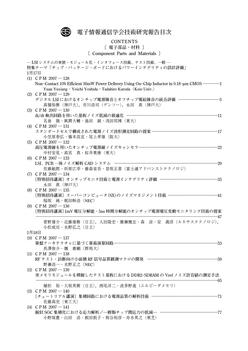

Print edition: ISSN 0913-5685 Online edition: ISSN 2432-6380

[TOP] | [2006] | [2007] | [2008] | [2009] | [2010] | [2011] | [2012] | [Japanese] / [English]

CPM2007-128

Non-Contact 10% Efficient 36mW Power Delivery Using On-Chip Inductor in 0.18-um CMOS

Yuan Yuxiang, Yoichi Yoshida, Tadahiro Kuroda (keio Univ.)

pp. 1 - 4

CPM2007-129

Integrated evaluation of on-chip power supply noise and off-chip electromagnetic noise on digital LSI

Yuki Takahashi (Kobe Univ.), Kouji Ichikawa (Denso), Makoto Nagata (Kobe Univ.)

pp. 5 - 10

CPM2007-130

ptimization of Active Substrate Noise Cancellng Technique Using Multi di/dt Detectors

Toru Nakura, Taisuke Kazama, Makoto Ikeda, Kunihiro Asada (The Univ. of Tokyo)

pp. 11 - 16

CPM2007-131

All Digital Gated Oscillator for Dynamic Supply Noise Measurement

Yasuhiro Ogasahara, Masanori Hashimoto, Takao Onoye (Osaka Univ.)

pp. 17 - 22

CPM2007-132

Design of an On-Chip Noise Canceller with High Voltage Supply Lines for Nanosecond-Range Power Supply Noise

Yasumi Nakamura, Makoto Takamiya, Takayasu Sakurai (Univ. of Tokyo)

pp. 23 - 27

CPM2007-133

LSI and PCB Unified Noise Analysis CAD System

Toshiro Sato, Hiroyuki Orihara, Shogo Fujimori, Masaki Tosaka (FATEC)

pp. 29 - 34

CPM2007-134

[Special Invited Talk]

On-chip monitors and power-supply integrity

Makoto Nagata (Kobe Univ.)

pp. 35 - 40

CPM2007-135

[Special Invited Talk]

Techniques for power supply noise management in the SX supercomputers

Jun Inasaka, Mikihiro Kajita (NEC Corp.)

pp. 41 - 46

CPM2007-136

[Special Invited Talk]

In-situ measurement of supply-noise maps with millivolt accuracy and nanosecond-order time resolution

Yusuke Kanno, Yuki Kondoh (HCRL), Takahiro Irita, Kenji Hirose, Ryo Mori, Yoshihiko Yasu (Renesas Technology, Corp.), Shigenobu Komatsu, Hiroyuki Mizuno (HCRL)

pp. 47 - 52

CPM2007-137

Arithmetic operation circuit based on abacus architecture

Syunsuke Nagasawa, Shugang Wei (Gunma Univ)

pp. 53 - 58

CPM2007-138

A compact RF signal quality measurement macro for RF test and diagnosis

Koichi Nose, Masayuki Mizuno (NEC)

pp. 59 - 64

CPM2007-139

A Method for Measuring Vref Noise Tolerance of DDR2-SDRAM on Test Board that Simulates Memory Module

Yutaka Uematsu, Hideki Osaka (Hitachi), Yoji Nishio, Susumu Hatano (Elpida)

pp. 65 - 69

CPM2007-140

[Tutorial Lecture]

Survey of Analysis Techniques for On-chip Power Distribution Networks

Takashi Sato (Tokyo Tech.)

pp. 71 - 76

CPM2007-141

Study on Low Stress Condition of Pseudo-SOC Integration Using Stress Analysis

Yutaka Onozuka, Hiroshi Yamada, Atsuko Iida, Kazuhiko Itaya, Hideyuki Funaki (Toshiba R & D Center)

pp. 77 - 82

CPM2007-142

An Extraction Method of Material Constants by Transmission Line Measurements

Hiroshi Toyao, Yoshiaki Wakabayashi (NEC)

pp. 83 - 86

CPM2007-143

A Package-on-Package using Coreless Substrate with Excellent Power Integrity

Kentaro Mori, Jun Sakai, Katsumi Kikuchi, Shinji Watanabe, Tomoo Murakami, Shintaro Yamamichi (NEC)

pp. 87 - 92

CPM2007-144

Assessment Test for Solder Joint Reliability in Mobile Products

Masazumi Amagai, Hiroyuki Sano (TI Japan)

pp. 93 - 98

CPM2007-145

Chip Thinning Technologies Realizing High Chip Strength

Shinya Takyu, Tetsuya Kurosawa, Noriko Shimizu, Susumu Harada (Toshiba Co.)

pp. 99 - 103

CPM2007-146

A multi-layer wafer-level 5-um-thick Cu wiring technology with photosensitive resin

Katsumi Kikuchi (NEC), Kouji Soejima (NECEL), Yasuhiro Ishii (NEC), Masaya Kawano (NECEL), Masayuki Mizuno, Shintaro Yamamichi (NEC)

pp. 105 - 110

CPM2007-147

A method of Ultra-fine Pad Interconnection using Electroless Deposition

Tokihiko Yokoshima, Yasuhiro Yamaji, Yuichiro Tamura, Katsuya Kikuchi, Hiroshi Nakagawa, Masahiro Aoyagi (AIST)

pp. 111 - 116

CPM2007-148

Reliability evaluation of lead free solder joint against vibration load under thermal circumstance

Michiya Matsushima (Osaka Univ.), Toshiyuki Hamano (ESPEC), Kiyokazu Yasuda, Kozo Fujimoto (Osaka Univ.)

pp. 117 - 122

Note: Each article is a technical report without peer review, and its polished version will be published elsewhere.