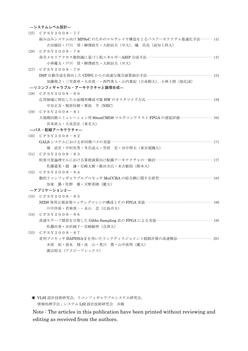

Print edition: ISSN 0913-5685 Online edition: ISSN 2432-6380

[TOP] | [2006] | [2007] | [2008] | [2009] | [2010] | [2011] | [2012] | [Japanese] / [English]

CPSY2008-53

動的リコンフィギャラブルプロセッサMuCCRA-3の実装と再構成オーバヘッドの削減

○佐野 徹・天野英晴(慶大)

pp. 1 - 6

CPSY2008-54

Evaluation of a Multicore Reconfigurable Architecture

○Vu Manh Tuan・Hiroki Matsutani・Naohiro Katsura・Hideharu Amano(Keio Univ.)

pp. 7 - 12

CPSY2008-55

デュアルV-th技術を用いた動的リコンフィギャラブルプロセッサの低消費電力化

○平井啓一郎・佐野 徹・加東 勝・天野英晴(慶大)

pp. 13 - 17

CPSY2008-56

FPGAアレイを用いてTFlopsを目指したポアソン方程式演算回路の実装と評価

○佐藤一輝・バートルスレン バルス・関根優年(東京農工大)

pp. 19 - 24

CPSY2008-57

メタスタビリティを利用した真性乱数生成回路のFPGAによる実装

○畑 尚志・市川周一(豊橋技科大)

pp. 25 - 30

CPSY2008-58

メッセージ駆動形IPコアインタフェースの一提案

○佐々木隆太・中村次男・冬爪成人・笠原 宏・田中照夫(東京電機大)

pp. 31 - 36

CPSY2008-59

9コンテキスト・プログラマブル光再構成型ゲートアレイとライター

○久保田慎也・渡邊 実(静岡大)

pp. 37 - 40

CPSY2008-60

4コンテキスト光再構成型ゲートアレイの実証

○間渕隆之・渡邊 実(静岡大)

pp. 41 - 44

CPSY2008-61

反転・非反転ダイナミック光再構成アーキテクチャの比較評価

○加藤進一・渡邊 実(静岡大)

pp. 45 - 50

CPSY2008-62

時間多重I/Oを考慮した回路分割手法

○磯村達樹(北九州市大)・稲木雅人(広島市大)・高島康裕(北九州市大)・中村祐一(NEC)

pp. 51 - 55

CPSY2008-63

FPGA向けテクノロジ・マッピングにおける深さ最小ネットワーク生成のための効率的なカット列挙手法

○高田大河・松永裕介(九大)

pp. 57 - 62

CPSY2008-64

任意精度計算機アーキテクチャの提案

○橋本将平・戸塚雄太・牧野政道・安田 光・中村次男・冬爪成人・笠原 宏(東京電機大)

pp. 63 - 68

CPSY2008-65

MXコアにおけるPE粒度変更による実行効率の改善

○溝上雄太・中野光臣・飯田全広・末吉敏則(熊本大)

pp. 69 - 74

CPSY2008-66

テスト用Linuxクラスタシステムの試作

○北野皓一(職能開発大)・寺本晃司(雇用・能力開発機構)・堀田忠義(職能開発大)

pp. 75 - 79

CPSY2008-67

高位合成システムCCAPのAMPマルチコアシステム設計のための拡張

○石守祥之・石浦菜岐佐(関西学院大)・冨山宏之(名大)・神原弘之(京都高度技研)

pp. 81 - 86

CPSY2008-68

制御のタイミングスキューおよびストールに基づくLSIチューニング

○上原八弓・金子峰雄(北陸先端大)

pp. 87 - 92

CPSY2008-69

フロアプランを考慮した高位合成のための高速なモジュール配置手法

○佐藤 亘・大智 輝・戸川 望・柳澤政生・大附辰夫(早大)

pp. 93 - 98

CPSY2008-70

アプリケーションプロセッサのための高速かつ最適なパイプライン構成を持つSIMD演算ユニット合成手法

○渡辺隆行・戸川 望・柳澤政生・大附辰夫(早大)

pp. 99 - 104

CPSY2008-71

順序回路の上位設計記述における等価性指定の自動化手法

○許 金美・西原 佑・松本剛史・藤田昌宏(東大)

pp. 105 - 110

CPSY2008-72

仕様から自動生成されたプロパティによるプロトコル変換機の形式的検証手法

○高 飛・西原 佑・松本剛史・藤田昌宏(東大)

pp. 111 - 116

CPSY2008-73

規則性予見演算器

○佐藤 仁・中村次男・冬爪成人・笠原 宏・田中照夫(東京電機大)

pp. 117 - 122

CPSY2008-74

GAを用いた演算増幅器の素子値最適化における主成分分析による探索効率の向上

○竹原裕司(豊橋技科大)・夏井雅典(東北大)・田所嘉昭(豊橋技科大)

pp. 123 - 128

CPSY2008-75

高精度RTLタイミングモデルの一検討

○中嶋将太・福井正博(立命館大)

pp. 129 - 134

CPSY2008-76

抽象化処理の相互作用による概念の創造過程 ~ 人間のように思考する電子頭脳 ~

○服部忠幸

pp. 135 - 140

CPSY2008-77

組み込みシステム向けMPSoCのためのマルチレイヤ構造をとるバスアーキテクチャ最適化手法

○吉田陽信・戸川 望・柳澤政生・大附辰夫(早大)・橘 昌良(高知工科大)

pp. 141 - 146

CPSY2008-78

命令メモリアクセス数削減に基づく低エネルギーASIP合成手法

○小林優太・戸川 望・柳澤政生・大附辰夫(早大)

pp. 147 - 152

CPSY2008-79

DSP自動合成を指向したCDFGからの高速な複合演算抽出法

加藤俊之・○三宅貴章・大亦真一・西門秀人・山内寛紀(立命館大)・小林士朗(旭化成)

pp. 153 - 158

CPSY2008-80

応用領域に特化した小面積再構成可能HWのカスタマイズ方式

○中谷正吾・梶原信樹・粟島 亨(NEC)

pp. 159 - 164

CPSY2008-81

大規模回路エミュレーション用90nm CMOSマルチコンテクストFPGAの遅延評価

○宮本直人・大見忠弘(東北大)

pp. 165 - 170

CPSY2008-82

GALSシステムにおける非同期バスの実装

○堀 武宏・中村次男・冬爪成人・笠原 宏・田中照夫(東京電機大)

pp. 171 - 176

CPSY2008-83

粒度可変論理セルにおける算術演算向け配線アーキテクチャの一検討

○佐藤嘉晃・趙 謙・尼崎太樹・飯田全広・末吉敏則(熊本大)

pp. 177 - 182

CPSY2008-84

動的リコンフィギャラブルプロセッサMuCCRAの結合網に関する研究

○加東 勝・佐野 徹・天野英晴(慶大)

pp. 183 - 188

CPSY2008-85

NIDS専用正規表現マッチングマシンの構成とそのFPGA実装

○川中洋祐・若林真一・永山 忍(広島市大)

pp. 189 - 194

CPSY2008-86

高速モチーフ探索を目指したGibbs Sampling法のFPGAによる実装

○佐藤由香・田沢純子・宮崎敏明(会津大)

pp. 195 - 199

CPSY2008-87

並列プロセッサDAPDNA-2を用いたリンクディスジョイント経路計算の高速解法

○木原 拓・清水 翔・高 山・荒川 豊・山中直明(慶大)・渡辺昭文(アイピーフレックス)

pp. 201 - 206

今後、次の点を修正する予定です。(1)欠けている表紙画像・奥付画像を補完いたします。(2)欠けている発行日の情報を補完いたします。

注: 本技術報告は査読を経ていない技術報告であり,推敲を加えられていずれかの場に発表されることがあります.