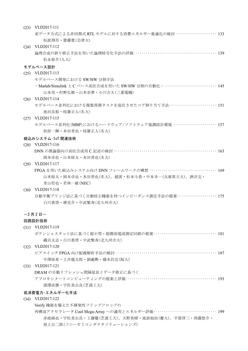

Print edition: ISSN 0913-5685 Online edition: ISSN 2432-6380

[TOP] | [2014] | [2015] | [2016] | [2017] | [2018] | [2019] | [2020] | [Japanese] / [English]

VLD2017-89

On Fast Computation of RBF Approximate Function by FPGA Implementation

Shogo Masuda, Shinobu Nagayama, Masato Inagi, Shin'ichi Wakabayashi (Hiroshima City Univ.)

pp. 1 - 6

VLD2017-90

On Memory Size Reduction of Programmable Hardware for Random Forest based Network Intrusion Detection

Binbin Xue, Shinobu Nagayama, Masato Inagi, Shin'ichi Wakabayashi (Hiroshima City Univ.)

pp. 7 - 12

VLD2017-91

k-Nearest Neighbor Search Hardware Using Locality Sensitive Hashing for High-Dimensional Data

Yuto Arai, Shin'ichi Wakabayashi, Shinobu Nagayama, Masato Inagi (Hiroshima City Univ.)

pp. 13 - 18

VLD2017-92

A fast routing method for multi-terminal nets using constraint satisfaction problem

Saki Yamaguchi, Yasuhiro Takashima (Univ. of Kitakyushu)

pp. 19 - 24

VLD2017-93

Amoeba-inspired SAT Solvers on FPGA through High Level Synthesis

Hoang Ngoc Anh Nguyen (Tokyo Tech), Masashi Aono (Keio Univ.), Yuko Hara-Azumi (Tokyo Tech)

pp. 25 - 30

VLD2017-94

Systematic Analysis Framework of Variables Significance towards Approximate Computing

Sara Ayman Metwalli, Yuko Hara-Azumi (Tokyo Tech)

pp. 31 - 36

VLD2017-95

Random Testing of Android Virtual Machine by Valid Dex File Generation

Hirofumi Ikeo, Ryotaro Shimizu, Nagisa Ishiura (Kwansei Gakuin Univ.)

pp. 37 - 42

VLD2017-96

Congestion Aware High Level Synthesis Design Flow with Source Compiler

Masato Tatsuoka, Mineo Kaneko (JAIST)

pp. 43 - 48

VLD2017-97

Development of Loop Flattening Tool that Reduces Cycle Overhead in Loop Pipelining of Nested Loops in High Level Synthesis

Daisuke Ishikawa, Kenshu Seto (TCU)

pp. 49 - 54

VLD2017-98

A Study on Quality Improvement of Frame Interpolation Method with High-Resolution and High-Frame Rate Video Using Foreground Elimination and Contour Extraction

Hirofumi Ihara, Takashi Imagawa (Ritumeikan Univ), Hiroki Uesaka, Shingo Kokami, Hiroshi Tsutsui, Yoshikazu Miyanaga (Hokkaido Univ), Hiroyuki Ochi (Ritumeikan Univ)

pp. 55 - 60

VLD2017-99

Architecture of Full-HD 60-fps Real-time Optical Flow Processor

Satoshi Kanda (Nihon Univ.), Kousuke Imamura, Yoshio Matsuda (Kanazawa Univ.), Tetsuya Matsumura (Nihon Univ.)

pp. 61 - 66

VLD2017-100

A Study of Acceleration Optimization for an EV Cart with a Lithium-ion Battery

Haruya Fujii, Yoshiki Tsuchida, Tomoki Abe, Lei Lin, Masahiro Fukui (Ritsumeikan Univ.)

pp. 67 - 72

VLD2017-101

Reconfiguration for Fault Tolerant FPGA Considering Incremental Multiple Faults

Cheng Ma, Mineo Kaneko (JAIST)

pp. 73 - 78

VLD2017-102

Reliability Evaluation of Mixed Error Correction Scheme for Soft-Error Tolerant Datapaths

Junghoon Oh, Mineo Kaneko (JAIST)

pp. 79 - 84

VLD2017-103

Evaluation of a Radiation-Hardened Method and Soft Error Resilience on Stacked Transistors in 28/65 nm FDSOI Processes

Haruki Maruoka, Kodai Yamada, Mitsunori Ebara, Jun Furuta, Kazutoshi Kobayashi (KIT)

pp. 85 - 90

VLD2017-104

Evaluation of Soft Error Tolerance on Flip-Flop depending on 65 nm FDSOI Transistor Threshold-Voltage

Mitsunori Ebara, Haruki Maruoka, Kodai Yamada, Jun Furuta, Kazutoshi Kobayashi (KIT)

pp. 91 - 96

VLD2017-105

A Study of Lithography Hotspot Detection Method Based on Feature Vectors Considering Distances between Wires

Gaku Kataoka, Masato Inagi, Shinobu Nagayama, Shin'ichi Wakabayashi (Hiroshima City Univ.)

pp. 97 - 102

VLD2017-106

Efficient Generation of Lithography Hotspot Detector based on Transfer Learning

Shuhei Suzuki, Yoichi Tomioka (UoA)

pp. 103 - 108

VLD2017-107

Clustering for Reduction of Power Consumption and Area on Post-Silicon Delay Tuning

Kota Muroi, Yukihide Kohira (Univ. of Aizu)

pp. 109 - 114

VLD2017-108

A Motif Extraction Method Using Monte-Carlo Tree Search and its Experimental Evaluation

Yusuke Yuasa, Shinobu Nagayama, Masato Inagi, Shin'ichi Wakabayashi (Hiroshima City Univ.)

pp. 115 - 120

VLD2017-109

(See Japanese page.)

pp. 121 - 126

VLD2017-110

An Evaluation of Graph Reduction Technique for Delay Insertion of General-Synchronous Circuit

Yuki Arai, Shuji Tsukiyama (Chuo Univ.)

pp. 127 - 132

VLD2017-111

A Study on Energy Optimization for Asynchronous RTL Models with Bundled-data Implementation

Shogo Semba, Hiroshi Saito (UoA)

pp. 133 - 138

VLD2017-112

Evaluating logic encryption methods using error correcting logic synthesis

Yusuke Matsunaga (Kyushu Univ.)

pp. 139 - 144

VLD2017-113

A SW/HW Partitioning for Model Based Design

-- A automated SW/HW partitioning using Matlab/Simulink and C based High Level Synthesis --

Ryo Yamamoto, Koki Murano, Ayumu Yamamoto, Yoshihiro Ogawa (Mitsubishi Electric)

pp. 145 - 150

VLD2017-114

Core allocation with mixed multirate tasks in model-based parallelization

Yoshihiro Ikeda, Masato Edahiro (Nagoya Univ)

pp. 151 - 156

VLD2017-115

Hardware/Software co-design environment in model-based parallelization (MBP)

Kazuki Kashiwabara, Shinya Honda, Masato Edahiro (Nagoya Univ.)

pp. 157 - 162

VLD2017-116

A C Description Approach for High Level Synthesis to Configure DNN Inference Circuit

Takuya Okamoto, Ryota Yamamoto, Shinya Honda (Nagoya Univ.)

pp. 163 - 168

VLD2017-117

A Concept of DNN Framework for Embedded System Using FPGA

Ryota Yamamoto, Takuya Okamoto, Shinya Honda (Nagoya Univ.), Qian Zhao, Toki Matsumoto, Yukikazu Nakamoto (Hyogo Univ.), Tamotsu Sakai, Tetsuya Aoyama, Kazutoshi Wakabayashi (NEC)

pp. 169 - 174

VLD2017-118

Impedance Evaluation Mechanism with Automatic Calibration based on Automatic Balanced Bridge

Takaaki Shirakawa, Sakai Ryosuke, Nakatake Shigetoshi (Univ. of Kitakyusyu)

pp. 175 - 179

VLD2017-119

On-chip and ultra low current measurement circuit based on potentiostat method

Daishi Isogai, Takaaki Shirakawa, Shigetoshi Nakatake (Univ. of Kitakyushu)

pp. 181 - 186

VLD2017-120

A study on interconnect delay computation for via-switch based FPGA

Yuki Nakazawa, Ryutaro Doi, Jaehoon Yu, Masanori Hashimoto (Osaka Univ.)

pp. 187 - 192

VLD2017-121

Approximate computing based on extension of DRAM refresh interval and data correction

Takamasa Fukasawa, Kimiyoshi Usami (SIT)

pp. 193 - 198

VLD2017-122

Implementation of Reconfigurable Accelerator Cool Mega-Array Using MTJ-based Nonvolatile Flip-Flop Enabling to Verify Stored Data

Junya Akaike, Kimiyoshi Usami, Masaru Kudo (SIT), Hideharu Amano, Takeharu Ikezoe (Keio Univ.), Keizo Hiraga, Yusuke Shuto, Kojiro Yagami (Sony SS)

pp. 199 - 204

VLD2017-123

Experimental study on power reduction by approximate computing with voltage over-scaling

Masahiro Sato, Yutaka Masuda, Masanori Hashimoto (Osaka Univ.)

pp. 205 - 210

VLD2017-124

Energy Reduction of Standard-Cell Memory Exploiting Selective Activation

Jun Shiomi, Tohru Ishihara, Hidetoshi Onodera (Kyoto Univ.)

pp. 211 - 216

VLD2017-125

[Invited Talk]

Cyber attacks and countermeasures for smart factories in the Age of Industry 4.0

Takeshi Yoneda (Mitsubishi Electric Corp.)

pp. 217 - 224

VLD2017-126

PL-PUF Implementation by Improvement of Capturing Timing Control Circuit

Yasuhiro Ogasahara, Yohei Hori, Hanpei Koike (AIST)

pp. 225 - 229

VLD2017-127

Modeling Attacks on Double-Arbiter PUF Using Deep Neural Network

Tomoki Iizuka, Hiromitsu Awano, Makoto Ikeda (UTokyo)

pp. 231 - 236

VLD2017-128

Machine Learning Attack Using Selectable Challenge Set for Feed-Forward PUF

Yusuke Nozaki, Masaya Yoshikawa (Meijo Univ.)

pp. 237 - 242

Note: Each article is a technical report without peer review, and its polished version will be published elsewhere.